В настоящее время становится ясно, что архитектура современных вычислительных систем, основанных на принципах Дж. фон Неймана имеет ряд существенных недостатков [1, 2]. Последовательная организация вычислительного процесса предполагает относительно низкую производительность системы. Другой недостаток обусловливает низкую эффективность использования дорогостоящей памяти при наличии одного процессора-ядра. Это связано с тем, что подавляющее большинство ячеек памяти в процессе работы бездействует и поэтому коэффициент использования аппаратуры будет очень низким [3]. Третий недостаток – разработчик вынужден подстраивать алгоритм решения задачи под «жесткую» структуру вычислительной системы.

С другой стороны, инженерная реализация нейронного компьютера У. МакКаллока и У. Питтса, описанная в «Логическом исчислении идей, имманентных нервной активности» [3, 4] в виде комплекса нейропроцессоров позволяет избавиться от перечисленных недостатков. В настоящее время имеется ряд архитектур нейрокомпьютера, разрабатываемых компаниями IBM, НТЦ “Модуль” и др., но трудностью разработки математического, алгоритмического и программного обеспечения для них является описание общих принципов архитектуры нейропроцессора, в связи с чем сформулирована цель исследования: системный анализ архитектуры нейропроцессора.

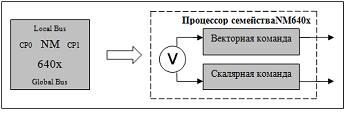

Процессоры семейства NM640x, также как и множество нейропроцессоров, обрабатывают данные параллельно по векторному принципу. Так как, нейропроцессор уже представляет собой параллельную систему [1], то получаемые системы при соответствующем уровне детализации могут рассматриваться как “системы в системе”. Поэтому рассмотрим отдельный процессор как вычислительную параллельную систему, применяя теоретико-множественный подход, и определим аналитические выражения оценок эффективности отдельного процессорного модуля (ПМ).

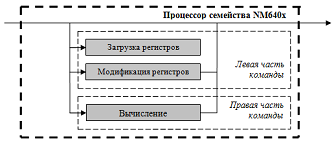

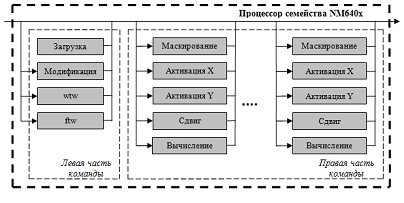

В процессоре семейства NM640x возможно два варианта команд (рисунок 1) [5-12]: скалярные команды – используются для подготовки данных к выполнению операции на векторном процессоре и векторные команды – основные операции процессора.

Рисунок 1 - Команды нейропроцессора семейства NM640x

Каждая из команд может выполнять несколько операций параллельно. Тогда каждый ПМ можно представить в виде системы параллельной обработки данных.

Анализ архитектуры нейропроцессора как системы параллельной обработки информации при выполнении скалярной команды

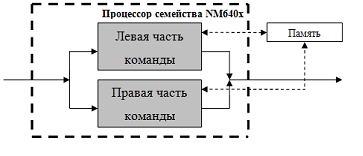

Скалярная команда нейропроцессора семейства NM640x имеет левую и правую часть, операции каждой части выполняются параллельно. Возможна пустая (nul) команда в левой или правой части.

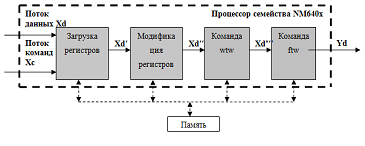

Структурная схема выполнения скалярной команды выглядит следующим образом (рисунок 2):

Рисунок 2 - Скалярная команда нейропроцессора

Левая часть содержит команды:

-

команды загрузки/записи, пересылки значений регистров;

-

команды адресной арифметики;

-

специальные скалярные команды;

-

команды безусловного и условного перехода;

-

команды перехода и возврата из подпрограммы или прерывания.

Правая часть содержит команды:

-

арифметические операции;

-

логические операции;

-

сдвиговые операции.

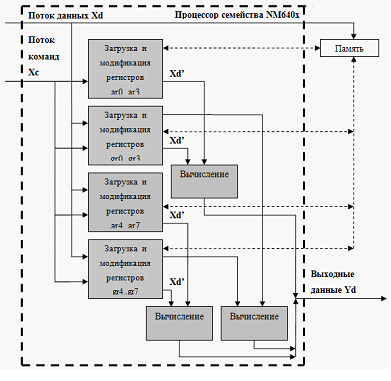

Детализированная схема выполнения скалярной операции представлена на рисунке 3:

Рисунок 3 – Детализированная схема выполнения скалярной операции

Команды для реализации блоков загрузки и модификации находятся в левой части команды. Блоки загрузки и модификации для различных регистров можно объединить в один или 2 отдельных модуля: загрузки и модификации, т.к. операция выполняется только для какого либо одного регистра (пары регистров). Блоки вычисления находятся в правой части команды и также могут быть объединены в один модуль. Тогда, исходя из приведенных выше схем, можно представить процессор при выполнении скалярной операции как параллельную систему следующим образом (рисунок 4):

Рисунок 4 – Выполнение скалярной команды процессора, представленное в виде параллельной системы

Анализ архитектуры нейропроцессора как системы параллельной обработки информации при выполнении векторной команды

Векторная команда нейропроцессора семейства NM640x также имеет левую и правую часть, возможна пустая команда в левой или правой части.

Левая часть содержит команды:

-

команды загрузки данных в векторный процессор;

-

команды выгрузки данных из векторного процессора;

-

специальные векторные команды.

Правая часть содержит команды:

-

взвешенное суммирование (матричное умножение);

-

маскирование;

-

арифметические операции;

-

логические операции;

-

операция циклического сдвига;

-

операции активации операндов;

-

выгрузка управляющих векторных регистров.

Кроме этого, как описано в первой главе, нейропроцессор семейства NM640x работает с “упакованными” данными – блоками по 64 бита каждый. Таким образом, в правой части за 1 такт может выполняться 2 операции по 32 бита, 8 операций по 8 бит и т.д. Максимальное количество выполняемых за один такт операций в векторном процессоре в правой части команды составляет 64 однобитных операции.

Сложность состоит в том, что трудно оценить число операций в той или иной команде, следовательно, необходимо рассматривать каждую операцию отдельно. Кроме того, операции имеют разное время выполнения (для операций с константой – 2 такта, для остальных операций – 1 такт).

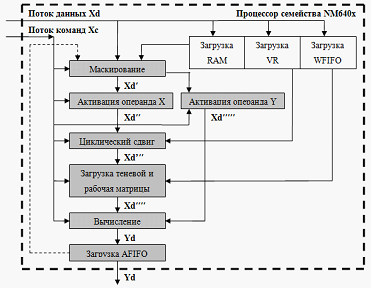

Детализируем выполнение левой части команды (рисунок 5).

Рисунок 5 – Детализированная схема выполнения левой части векторной команды

Детализируем выполнение правой части команды (рисунок 6).

Рисунок 6 – Детализированная схема выполнения правой части векторной команды

Исходя из приведенных схем, ПМ при выполнении векторной команды, можно представить в виде параллельной системы (рисунок 7).

Рисунок 7 – Выполнение векторной команды процессора, представленного в виде параллельной системы

Заключение:

Таким образом, были рассмотрены вопросы анализа нейропроцессорных устройств, принцип функционирования которых основан на принципах мышления человека. Показаны особенности структуры вычислителя нейрокомпьютера, благодаря которому достигается высокий уровень распараллеливания вычислительных операций.

Библиографический список

- Ruchkin V., Romanchuk V. and Sulitsa R.. Clustering, Restorability and Designing Of Embedded Computer System Based On Neuroprocessors // Proceedings of the 2nd Mediterranean Conference on Embedded Computing (MECO). – Budva, Montenegro, 2013. – С.58-62.

- Галушкин А.И., Нейрокомпьютеры. Кн.3. – М: ИПРЖР, 2000. – 528 с.

- Галушкин А.И., Судариков В.А., Шабанов Е.В. Нейроматематика: Методы решения задач на нейрокомпьютерах.- М: Препринт, 1990. – 440 с.

- Злобин В.К., Григоренко Д.В., Ручкин В.Н., Романчук В.А. Кластеризация и восстанавливаемость нейропроцессорных систем обработки данных // Известия тульского государственного университета. Технические науки. – Тула : Издательство ТулГУ, 2013. – Вып.9. – Ч.2. – С.125-135.

- Романчук В.А., Ручкин В.Н., Фулин В.А. Разработка модели сложной нейропроцессорной системы // Цифровая обработка сигналов. – Рязань : Информационные технологии, 2012. – №4. – С.70–74.

- Романчук В.А., Ручкин В.Н. Алгоритмы анализа вычислительных структур на базе нейропроцессоров // Вестник РГРТУ. – Рязань : РГРТУ, 2012. – №2. – Вып.40. – С.60–66.

- Романчук В.А., Ручкин В.Н. Оценка результатов моделирования вычислительных систем на базе нейропроцессоров // Известия тульского государственного университета. Технические науки. – Тула : Издательство ТулГУ, 2013. – Вып.9-2 – С.194-203.

- Романчук В.А., Лукашенко В.В. Разработка математической модели реструктуризуемого под классы задач, виртуализируемого кластера GRID-системы на базе нейропроцессоров // Вестник РГУ имени С.А.Есенина. – Рязань : РГУ имени С.А.Есенина, 2014. – №1(42). – C. 177- 182.

- Романчук В.А. Разработка алгоритмов определения связей элементов вычислительной структуры на базе нейропроцессоров // Информатика и прикладная математика : межвуз. сб. науч. тр. – Рязань : РГУ имени С.А.Есенина, 2011. – Вып.17. – С.102–105.

- Романчук В.А. Оптимизация программных и аппаратных средств сложных вычислительных систем на базе нейропроцессоров // Моделирование, оптимизация и информационные технологии. – 2015. – №1(8) 3 [Электронный ресурс]. URL: http://moit.vivt.ru/wp-content/uploads/2015/03/Romanchuk_1_15_1.pdf

- Романчук В.А. Моделирование нейропроцессорных систем // Отраслевые аспекты технических наук : научно-практический журнал. – Москва : ИНГН, 2013. – №10(34). – С.19-24.

- Романчук В.А., Лукашенко В.В. Модель описания функционирования нейропроцессора как сложной параллельной системы // Автоматизация и управление в технических системах. – 2015. – № 2; URL: auts.esrae.ru/14-266.

- Романчук В.А. Инновационный программный комплекс моделирования вычислительных систем на базе нейропроцессоров “НейроКС” // Современные научные исследования и инновации. – Декабрь, 2012 [Электронный ресурс]. – URL: http://web.snauka.ru/issues/2012/12/19407.

- Романчук В.А. Логическое проектирование вычислительных систем на базе нейропроцессоров // Современные научные исследования и инновации. 2014. № 12 [Электронный ресурс]. URL: http://web.snauka.ru/issues/2014/12/41496.